V2U3X8-PCIE8XE104

Octad Channel 8-port (1-port x 8) USB 3.0 (USB 3.1 Gen 1) to PCI Express x8 Gen 2 Host Card

Main > Product > Frame Grabbers & Interface Cards > USB3 Frame Grabber > PCIe x8 >V2U3X8-PCIE8XE104

V2U3X8-PCIE8XE104

|

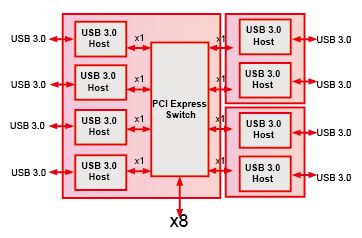

V2U3X8-PCIE8XE104 is designed with Two key components.

Utilizing the standard PCI Express Switch, the 16-Lane/16-Port PCI Express Switch provides the most efficient fan-out solution for integrating Eight PCI Express to USB 3.0 Single Chip Host controllers into a small board design. Each USB 3.0 to PCI Express Single Chip Host controller takes advantages of 5 Gbps burst rate of 8-lane PCI Express bus in both directions and is fully compliant with PCI Express Base specification r2.0. This solution provides full PCI Express and USB 3.0 functionality and performance. The design supports Per Port Power Switching and Over-Current Notification. The 2.0A (70mΩ on-resistance) Single Channel Current-Limited Power Switch (UL File Number E322375) has fast short-circuit Response time for improved overall system robustness, and have integrated output discharge function to ensure completely controlled discharging of the output voltage capacitor. They provide a complete protection solution for applications subject to heavy capacitive loads and the prospect of short circuit, and offer reverse current blocking, over-current, over-temperature and short-circuit protection, as well as controlled rise time and under-voltage lockout functionality. |

| The Highlight Features |

|

| Model | V2U3X8-PCIE8XE104 |

|---|---|

| PCI Express | Standards Compliant PCI Express Base Specification r2.0 (Backwards compatible with PCIe r1.0a/1.1) PCI Power Management Spec r1.2 Microsoft Vista Compliant Supports Access Control Services Dynamic link-width control Dynamic SerDes Speed Control High Performance Non-blocking internal architecture Full line rate on all ports Cut-Thru latency: 160ns for Link widths of x4 to x1 Maximum Payload Size – 2,048 bytes Read Pacing (intelligent bandwidth allocation) Dual Cast Dynamic Buffer Pool Architecture for faster credit updates PCI Express Power Management Link power management states: L0, L0s, L1 Device power management states: D0 and D3hot Active State Power Management (ASPM) Quality of Service (QoS) Two Virtual Channels (VC) per port Eight Traffic Classes per port Weighted Round-Robin Port & VC Arbitration |

| USB Features | Compliant with USB 3.0 Specification Revision 1.0 Compliant with Intel’s eXtensible Host Controller Interface (xHCI) specification Revision 1.0 Supports UASP (USB Attached SCSI Protocol) Each USB port supporting SS/HS/FS/LS data rates (5Gbps/480Mbps/12Mbps/1.5Mbps) |

| USB Data Transfer Rate | Low-speed (1.5 Mbps) Full-speed (12.0 Mbps) High-speed (480.0 Mbps) Super-speed (5.0 Gbps) |

| USB Ports | Eight independent USB 3.1 Gen 1 Cable Ports (Type-C Receptacle) Provides USB 3.1 Gen 1 Type-C cable port lock mechanism USB VBUS: USB Type-C Current Mode (1.5A@5V)  |

| VBUS Power Switch | 2.0A (70mΩ on-resistance) Single Channel Current-Limited Power Switch (UL File Number E322375) |

| USB Bus Power Input | 12V Step-Down to 5V from the following source, Either PCIe Edge Connector or Auxiliary Power Connector (J1:IDE 4-pin or J2:SATA 15-pin) |

|

Computer with PCI Express slot ( x8, x16) Note: |

|

|

|

|

|

|