V2U3X4-PCIE4XE312

Quad channel 16-port (4-port x 4) USB 3.0 to PCI Express x4 Gen 2 Host Card

Main > Product > Frame Grabbers & Interface Cards > USB3 Frame Grabber > PCIe x4 > V2U3X4-PCIE4XE312

V2U3X4-PCIE4XE312

|

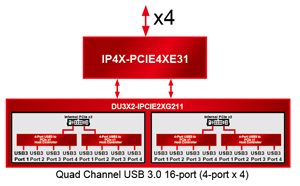

The V2U3X4-PCIE4XE312 is an Quad channel 16-port (4-port x 4) USB 3.0 to PCI Express x4 Gen 2 Host Card. V2U3X4-PCIE4XE312 is integrated by the following three key parts (V2IP4X-PCIE4XE31, V2DU3X2-IPCIE2XG211, V2CB-00592).

Utilizing the standard PCI Express Switch, the 8-Lane/5-Port PCI Express Switch provides the most efficient fan-out solution for integrating Quad PCI Express to USB 3.0 Single Chip Host controllers into a small board design. Each USB 3.0 to PCI Express Single Chip Host controller takes advantages of 5 Gbps burst rate of 4-lane PCI Express bus in both directions and is fully compliant with PCI Express Base specification r2.0. This solution provides full PCI Express and USB 3.0 functionality and performance. |

The Highlight Features

- 5.25″ ODD Form Factor

- Host Bus: PCIe x4 Gen 2 (5.0 GT/s)

- Compliant with PCI Express Base Specification Revision 2.0

- Quad independent USB 3.0 Host Controllers

- Sixteen USB 3.0 Cable Ports (A-type Receptacle)

-

- Provides USB 3.0 cable port lock mechanism

USB 3.0 Standard A-type lock mechanism -

| Model | V2U3X4-PCIE4XE312 |

|---|---|

| Upstream PCIe interface | 4-lane PCI Express : PCIe Gen 1 (2.5GT/s) : PCIe Gen 2 (5.0GT/s) |

| Downstream PCIe interface | Two IOI Proprietary Dual-lane Internal PCIe Ports (PCIe-1~2) :10X2_19pin Header (Pitch=2.0mm) :2-Lane PCIe (Two PCIe x1) Each Dual-lane Internal PCIe Port :PCIe Gen 1 (2.5GT/s) :PCIe Gen 2 (5.0GT/s) |

| Key Features | Standards compliant :Compliant with PCI Express Base Specification Revision 2.1 :Compliant with PCI Express CEM Specification Revision 2.0 :Compliant with PCI-toPCI Bridge Architecture Specification Revision 1.2 :Compliant with Advanced Configuration Power Interface (ACPI) Specification :PCI Power Management Spec r1.2 PCI Express Power Management : link power management states: L0, L0s, L1, L2/L3 Ready, and L3 : Device states: D0 and D3hot : Active state power management for L0s and L1 states Port Arbitration Round Robin (RR) and Weighted RR and Time-based Weighted RR Extended Virtual Channel capability :Two Virtual Channels (VC) and Eight Traffic Class (TC) support :Disabled VCs’ buffer is assigned to enabled VCs for resource sharing :Independent TC/VC mapping for each port :Provides VC arbitration selection: Strict Priority, Round Robin (RR) and Programmable Weighted Round-Robin Supports Isochronous Traffic : Isochronous traffic class mapped to VC1 only : Strict time based credit policing Supports “Cut-through”(Default) as well as “Store and Forward” mode for switching packets Peer-to-peer switching between any two downstream ports Supports up to 512-byte maximum payload size (setting to 256-byte) Enhanced Features :150ns typical latency for packet running through switch without blocking :Supports Access Control Service (ACS) for peer-to-peer traffic :Supports Address Translation (AT) packet for SR-IOV application :Supports OBFF and LTR |

| Computer Platform Requirements | Desktop computer equipped with a PCIe 2.0/3.0 x4, x8, x16 slot |

| Physical Dimensions | 64.5(H)x81(L)mm NW: 43.6g |

Note: |

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||

|

* Specifications subject to change without prior notice